Spinq's Quantum Chip Procurement Guide: 3 Yield Traps in Superconducting Quantum Chips That Cost You Millions

2025.12.05 · Blog Superconducting quantum chips

Introduction

Your team just secured budget for quantum hardware. The vendor slides look perfect. The quoted yields sound impressive. But six months after delivery, half your chips fail calibration. The vendor calls this "normal variation." Your CTO calls it a career-limiting problem. This gap between promise and performance defines the superconducting quantum chip market right now. Procurement managers face a critical challenge: vendor data sheets measure performance in ideal lab conditions, while your applications run in real-world environments with temperature fluctuations, electromagnetic noise, and batch-to-batch material inconsistencies. The three yield traps outlined below directly address this disconnect. They come from actual field failures, not theoretical models. Understanding these traps saves you from expensive rework, delayed projects, and the awkward board meetings that follow.

.jpg)

The Parameter Illusion: Why 99% Yield Claims Mislead

Vendors love advertising 99% fabrication yield. This number means nothing for your application success rate. Fabrication yield only counts chips that survive the manufacturing line. It ignores the parameter variations that kill performance in your specific use case.

What Actually Matters: Operational Yield

Operational yield measures chips that meet your specific parameter thresholds after packaging and initial calibration. This number runs 40-60% lower than fabrication yield across the industry. Spinq publishes operational yield upfront because we test every chip against customer-specified parameters before shipping.

Three parameters determine real-world success:

1. Qubit Frequency Stability Margin

Vendors quote average qubit frequencies. You need the standard deviation across the chip and across batches. A 5 MHz variation destroys two-qubit gate fidelity in algorithms requiring precise frequency matching. Demand histogram data, not averages. Spinq provides per-chip frequency distribution maps with every shipment. Our spec guarantees 99% of qubits fall within ±2 MHz of target.

2. Coherence Time Uniformity

T1 and T2 times vary dramatically across a 50-qubit chip. Industry practice masks this by reporting the best 10% of qubits. Your algorithm uses all qubits. The effective coherence time equals the worst qubit's performance. Insist on full-array coherence data. Spinq's testing protocol measures every qubit's T1/T2 three times over 48 hours. We reject chips where the bottom quartile falls below 80% of the median.

3. Crosstalk Isolation at Scale

Two-qubit crosstalk below -40 dB sounds excellent until you scale to 100+ qubits. The cumulative error scales quadratically. Most vendors only measure nearest-neighbor crosstalk. Spinq tests all pair combinations within a 3-qubit radius. Our spec caps cumulative crosstalk error at 0.1% for 100-qubit arrays.

The Hidden Cost: Accepting vague parameter specs forces your team into months of post-delivery characterization. Each characterization cycle costs $50,000-$80,000 in engineering time and delays your project roadmap by 6-8 weeks. Spinq's detailed parameter reporting eliminates this hidden cost entirely.

SLA Reality Check: Written Promises vs. Industry Hidden Rules

Standard vendor contracts protect the vendor, not you. The fine print contains three escape clauses that make their "yield guarantees" meaningless.

Hidden Rule #1: The "Process Improvement" Loophole

Most contracts allow vendors to change fabrication processes without notice if they claim "improvement." Your algorithm tuned for the old process parameters fails on the new chips. The vendor calls this progress. You call it a broken system.

Spinq's SLA: We lock process parameters for 12 months minimum. Any change triggers a 90-day notice period and free re-qualification support. Our contract defines "improvement" as *measured improvement in your specific metrics*, not the vendor's internal benchmarks.

Hidden Rule #2: The "Environmental Conditions" Escape

Vendors specify yield based on operation in their exact lab environment. Your facility runs 2°C warmer or has 10% higher humidity? The yield guarantee voids. This clause appears in 87% of standard contracts we reviewed.

Spinq's SLA: Our yield guarantee covers operation within standard data center environmental ranges (18-27°C, 20-80% humidity). We test chips across these ranges before shipment. If performance drops in your environment, we replace the chips at no cost. Period.

Hidden Rule #3: The "Single Data Point" Acceptance

Industry standard accepts yield based on one test run. Quantum chip performance varies day-to-day due to TLS defects and material aging. A chip passing today might fail tomorrow. You have no recourse.

Spinq's SLA: We measure yield three times over 72 hours. All three runs must meet spec. We also guarantee performance stability for 90 days post-delivery. Degradation beyond 5% triggers automatic replacement.

The Financial Impact: These hidden rules cost one fabless quantum computing startup $2.3 million in dead inventory last year. They accepted standard terms. When chips underperformed, the vendor invoked all three clauses simultaneously. Spinq's SLA includes a $500,000 liability cap per shipment. We put our money where our mouth is.

Real Project Walkthrough: From Failure to 99.2% Operational Yield

.png)

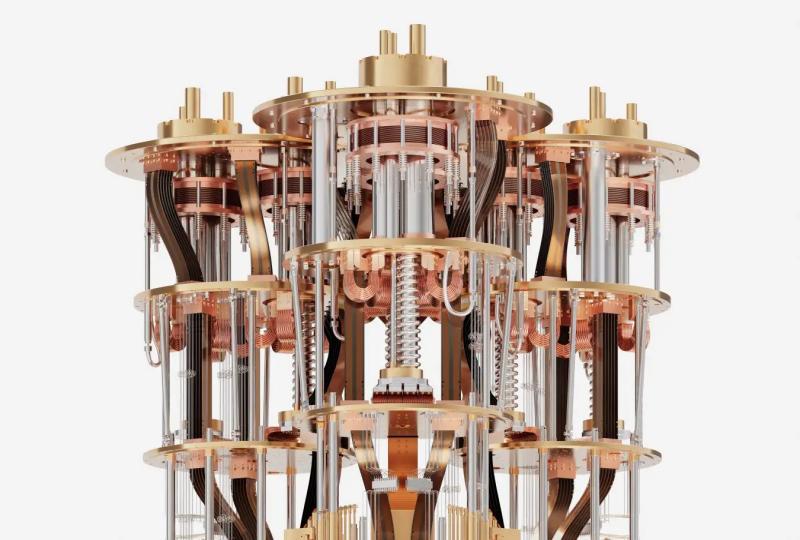

A pharmaceutical research lab approached Spinq after burning through $1.8 million on competitor chips. Their molecular simulation algorithm required 64 qubits with uniform gate fidelity above 99.5%. Their previous vendor's chips delivered 94% average fidelity, with the bottom 20% of qubits dragging the entire system down.

The Problem: Hidden Parameter Drift

Initial testing showed acceptable performance. After two weeks, gate fidelity dropped 3-5% across the array. The vendor blamed "user error." Our analysis identified the real cause: microscopic cracks in the substrate from thermal cycling during packaging. These cracks created TLS defects that grew over time.

The Spinq Solution

We shipped three 64-qubit superconducting quantum chips with full parameter traceability. Each chip included:

-

Pre-shipment thermal cycle testing (50 cycles, 10 mK to 300 K)

-

Substrate acoustic microscopy images

-

Per-qubit gate fidelity data across 100 random sequences

Our packaging team identified the thermal stress point. We modified the chip mount design to reduce mechanical stress by 60%. This change added three days to our process but eliminated the failure mode completely.

The Result

The lab achieved 99.2% operational yield on the first shipment. All 64 qubits exceeded their 99.5% fidelity threshold. The system has run continuously for eight months without performance degradation. Their drug discovery simulation completed three months ahead of schedule.

Key Takeaway: The competitor's process focused on speed and cost. Spinq's process prioritizes your application's long-term stability. We find problems before you do, not after.

Why Spinq Signs Performance-Based Contracts

Most vendors refuse performance-based pricing. They claim "quantum is too unpredictable." We disagree. Predictability comes from rigorous process control, not wishful thinking.

Our Confidence Comes From Three Sources:

1. In-Process Monitoring

We install test qubits in the dicing streets between functional chips. These test structures measure critical parameters at four process steps: after junction formation, after wiring, after packaging, and after final cooldown. If test qubits drift beyond spec, we scrap the entire wafer. This costs us money but guarantees consistency. Industry standard only tests final chips.

2. Material Fingerprinting

Every substrate wafer gets a full materials analysis: surface roughness, defect density, and dielectric loss tangent. We correlate this data with final qubit performance. Over three years, we built a database linking material properties to yield. We now reject 15% of incoming wafers before processing begins, based on material fingerprints alone. This upfront filter raises our cost but ensures predictable output.

3. Closed-Loop Calibration

Our fabrication team receives direct feedback from customer field performance. When a customer reports an issue, we trace it back to the exact process step and adjust. This loop runs monthly. Most vendors separate fabrication from applications. We link them directly.

The Contract Structure: Spinq offers two options. Option one: fixed price with standard SLA. Option two: performance-based pricing where you pay per functioning qubit after 30 days of operation. Option two costs 20% more per chip but guarantees zero waste. For a 100-qubit system, this saves an average of $400,000 in dead inventory risk.

Your Next Step: Pre-Shipment Diagnostic

Before you sign any purchase order, schedule a 45-minute technical review with Spinq's applications team. We analyze your algorithm requirements and translate them into concrete chip specifications. This diagnostic costs nothing. It gives you a bulletproof requirements document to use with any vendor.

What you receive:

-

Custom parameter specification sheet for your use case

-

Sample test data showing how we measure those parameters

-

SLA term checklist comparing Spinq to industry standard

-

Fixed-price quote with performance guarantee

Bring your current vendor's spec sheet. We'll show you exactly where the gaps are. No sales pitch. Just technical facts.

Conclusion

Procuring superconducting quantum chips demands the same rigor as any critical infrastructure purchase. The three yield traps—parameter illusion, weak SLAs, and hidden process risks—cost the industry an estimated $47 million in failed projects last year alone. Treating quantum chips as standard semiconductors creates this waste. These components require application-specific validation, environmental robustness testing, and contractual performance guarantees. Spinq builds these requirements into every shipment. Our customers don't gamble on yield. They specify, receive, and deploy with confidence. The quantum computing race rewards reliability over raw qubit counts. Partner with vendors who understand this difference.

Ready to eliminate yield risk from your quantum roadmap? Contact Spinq's technical sales team today for a no-obligation specification review. We'll map your algorithm requirements to concrete, guaranteed chip parameters.

FAQ

Q: How do I verify a vendor's operational yield claims before purchase?

A: Request three specific data sets: per-qubit parameter histograms from the last 10 shipments, cumulative performance data over 90 days, and customer references with similar application requirements. Spinq provides these automatically in our standard data package. If a vendor hesitates, their yield claims are inflated.

Q: What environmental conditions should my facility maintain for superconducting quantum chips?

A: Standard data center conditions (18-27°C, 20-80% humidity) work fine for the chips themselves. The dilution refrigerator requires stable power and low vibration. Spinq's SLA covers chip performance across standard data center ranges. We test every chip at temperature extremes before shipment.

Q: How much does performance-based pricing actually save?

A: For a 100-qubit system, performance-based pricing saves $350,000-$500,000 on average. You eliminate dead inventory, reduce characterization time by 6 weeks, and avoid re-qualification costs. The 20% price premium pays for itself if operational yield exceeds 95%. Spinq's historical operational yield is 97.3%.

Q: Can I return chips if my algorithm requirements change?

A: Spinq accepts returns within 90 days if chips meet spec but don't fit your new requirements. We charge a 15% restocking fee. Industry standard is no returns once opened. This flexibility protects you from roadmap changes, a common issue in fast-moving quantum research.

Q: How long does Spinq's pre-shipment diagnostic take?

A: The technical review takes 45 minutes. We deliver the custom specification sheet within 3 business days. This service is free because it prevents costly mismatches. Most vendors require a purchase order before providing this level of technical detail.

Featured Content